| 0907432 Computer Design (Fall 2013)<br><u>Midterm Exam</u> |                               |       |                                 |     |        |                |       |       |             |      |       |            |       |        |                          |

|------------------------------------------------------------|-------------------------------|-------|---------------------------------|-----|--------|----------------|-------|-------|-------------|------|-------|------------|-------|--------|--------------------------|

| 1                                                          | الشعبة:                       | رقم   |                                 |     | لمسلي  |                |       |       |             |      |       |            |       | م:     | الاس                     |

| Instruction<br>the space p                                 |                               |       | -                               |     | space  |                | vide  | d. N  |             |      |       |            |       |        | =======<br>l problems in |

| -                                                          | •                             |       | typical 5-s<br>the proces       |     |        | -              |       |       |             |      |       | -          |       |        | to solve data            |

|                                                            |                               |       | am below t<br>nstructions       |     | ut hov | w ma           | any c | cycle | s are       | need | led b | y thi      | s pro | ocesso | r to execute<br>[3 marks |

|                                                            |                               |       |                                 |     | 1      | 2              | 3     | 4     | 5           | 6    | 7     | 8          | 9     | 10     |                          |

|                                                            | addi                          | \$s1, | \$s1,-4                         |     | F      | D              | E     | M     | W           |      |       |            |       |        |                          |

|                                                            | bne                           | \$s1, | \$zero,                         | -20 |        | F              | D     | D     | E           | Μ    | W     |            |       |        |                          |

|                                                            | RF                            |       |                                 |     | 7      |                |       |       |             |      |       |            |       |        |                          |

|                                                            | t are the c<br><b>egWrite</b> |       | ns to stall the <b>E.Rd = D</b> |     |        | r this<br>D.br |       |       | ard?<br>and |      | E.Rd  | <b>≠ 0</b> |       |        | [3 marks                 |

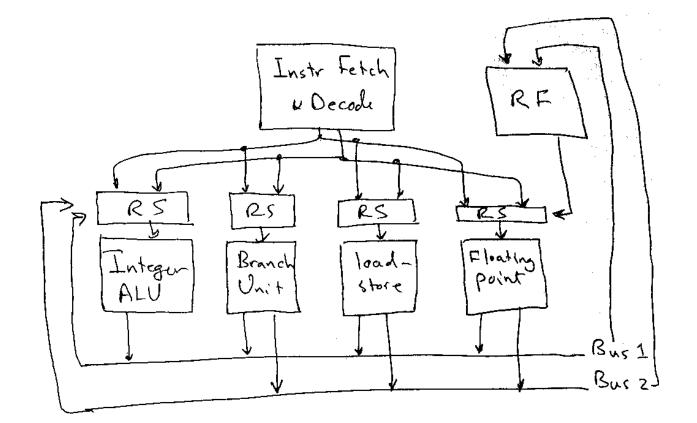

**Q2.** Draw a superscalar processor that can fetch, issue, and write back two instructions per cycle. Assume that this processor supports dynamic scheduling and allows out-of-order execution using reservation stations. Assume also that it has *out-of-order completion* and has the following functional units: integer ALU, branch unit, load-store unit, and floating-point unit. *Show all main busses including the busses from and to the register file*.

[10 marks]

Q3. Assume that you have a two-way associative cache. Also assume that the cache size is 8 KB and the block size is 16 bytes.

A) How many blocks does this cache have?

[2 marks]

8 KB / 16 B = 512 blocks

[2 marks]

B) What is the width of the cache index field?

[2 marks]

Sets = 512 blocks / 2 = 256 sets

<index> = lg2 256 = 8 bits

C) Complete the following table that shows the byte addresses of six accesses to this cache in hexadecimal. Assume that the cache was empty before these accesses and that the cache uses the LRU replacement. For every byte address, specify its cache index value, whether the access is a hit or miss, and the tag contents of the affected cache block after performing the access.

[6 marks] **Tag Contents** Tag Contents Cache Index Hit or miss Byte Address Set 0 Set 1 AABBCC00 **C0** Miss AABBC EEDDCC08 C0 Miss AABBC EEDDC C0 EEDDCC00 Hit AABBC EEDDC **C0** AABBC EEDDC AABBCC0C Hit C0 FF00CC04 Miss AABBC FF00C EEDDCC00 **C0** Miss EEDDC FF00C