## **Problems with Pipelining**

- Exception: An unusual event happens to an instruction during its execution

- Examples: divide by zero, undefined opcode

- Interrupt: Hardware signal to switch the processor to a new instruction stream

- Example: a sound card interrupts when it needs more audio output samples (an audio "click" happens if it is left waiting)

- Problem: It must appear that the exception or interrupt must appear between 2 instructions (I<sub>i</sub> and I<sub>i+1</sub>)

- The effect of all instructions up to and including l<sub>i</sub> is totalling complete

- No effect of any instruction after I<sub>i</sub> can take place

- The interrupt (exception) handler either aborts program or restarts at instruction I<sub>i+1</sub>

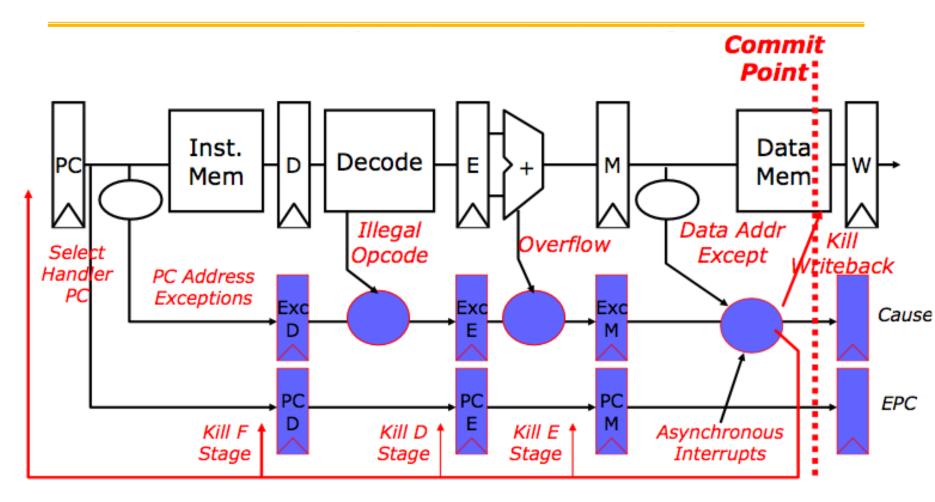

## **Precise Exceptions in Static Pipelines**

Key observation: architected state only change in memory and register write stages.